Sehr geehrte Investierende und Freunde/Freundinnen von APUS Capital,

wir alle kennen das Märchen von Hans Christian Andersen vom Entlein, das schließlich zu einem stolzen Schwan wird. Diese Geschichte von Andersen können wir oft im realen Leben beobachten. Aus dem Teenager wird ein attraktiver junger Erwachsener, aus dem alten Haus nach umfassender Sanierung ein Schmuckstück. Auch an der Börse mausert sich das eine oder andere Unternehmen vom Mauerblümchen zum Börsenstar. Hierfür kann es viele Gründe geben: Sich verändernde Märkte, neue gesetzliche Vorgaben, innovative Produkte mit erheblichem Wachstumspotential, geschickte Übernahmen, Partnerschaften oder neue Manager. Häufig kommen gleich mehrere dieser Faktoren zusammen. Wir bei APUS suchen genau nach diesen Unternehmen, die sich vom Entlein zum stolzen Schwan entwickeln. Die Kurse dieser Unternehmen profitieren nicht nur von der beschleunigten Umsatz- und Gewinndynamik, sondern auch von einer höheren Bewertung. Unsere Zielformulierung von 8-10% p.a. als durchschnittliche jährliche Rendite unseres APUS Capital ReValue Fonds bei seiner Auflage im Jahr 2011, haben wir seither erfüllt (siehe beiliegendes Factsheet).

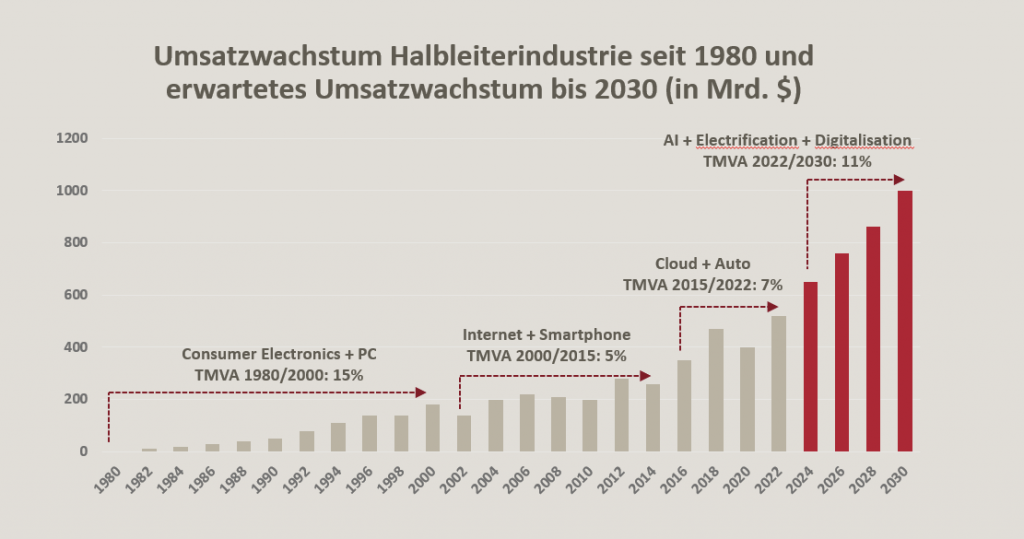

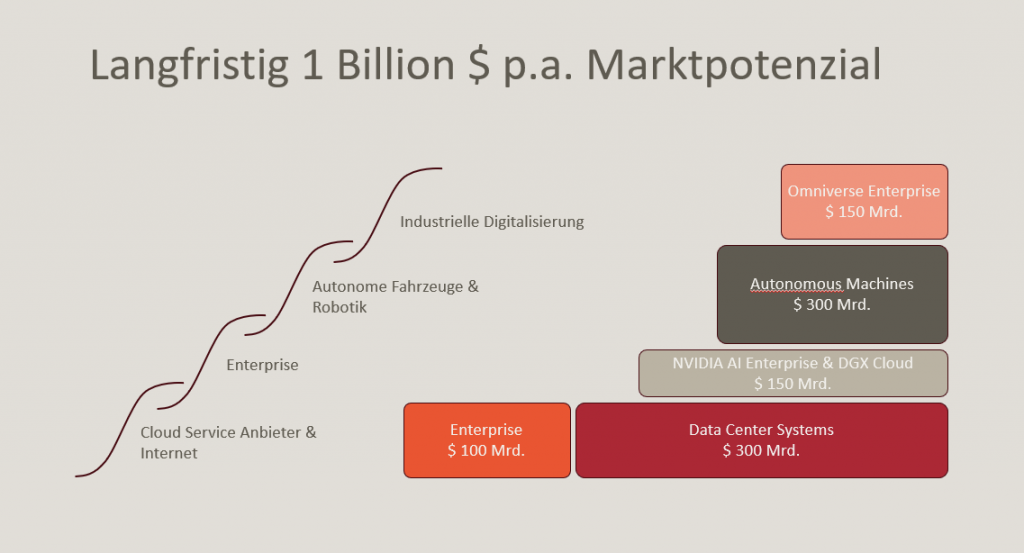

Ein Sektor, der von den großen Megatrends unserer Zeit wie Digitalisierung, alternativen Energien, neuen Mobilitätskonzepten, aber auch innovativen technologischen Lösungen in der Medizintechnik besonders profitiert, ist der Halbleitersektor. All diese Anwendungen brauchen „Unmengen“ an Halbleitern, warum die Zuwachsraten des Chipsektors in den kommenden Jahren deutlich höher ausfallen werden, als in den beiden Dekaden zuvor. Der durch ChatGPT ausgelöste Boom im Einsatz von künstlicher Intelligenz sollte das Wachstum sogar noch über die im unteren Schaubild angenommene Wachstumsrate von 11% hinaus beschleunigen. So soll laut dem Unternehmen AMD der Markt für KI-Chips alleine bis 2027 auf 400 Mrd. USD anwachsen. Nvidia sieht sogar langfristig für den KI-Markt in all seinen Ausprägungen ein mögliches Potential von einer Billion USD, also der Marktgröße, die der gesamte Halbleitermarkt nach früheren Schätzungen bis 2030 erreichen sollte.

Vor diesem Hintergrund sehen wir den Halbleiterbereich trotz einer gewissen Zyklik als einen, wenn nicht sogar den attraktivsten Sektor für unseren Investmentansatz in den kommenden Jahren. Dies vor dem Hintergrund, dass sich auch bei unserem regionalen Fokus auf Europa zahlreiche gut positionierte Unternehmen finden lassen. Diese profitieren insbesondere von zwei großen technologischen Trends innerhalb der Halbleiterindustrie, die erst am Anfang eines großen Wachstums stehen:

- Der Einsatz innovativer Materialen mit vorteilhafteren Eigenschaften als das klassische Silizium. Die Potentiale von Halbleitern auf Siliziumkarbid oder Galliumnitrid-Basis, gerade, wenn es um Energieeffizienz geht, haben wir Ihnen in unserem Investorenbrief vom Oktober 2023 aufgezeigt.

- Der zweite Megatrend der Halbleiterindustrie heißt „Advanced Packaging“ und ist wahrscheinlich noch bedeutender als der Einsatz neuer Materialien. Daher möchten wir diese Technologien im Folgenden etwas genauer beleuchten.

Die klassische auf Silizium basierende Halbleitertechnologie stößt zunehmend an ihre physikalischen Grenzen. Und dies ist kein ganz neues Phänomen: So konnte zum Beispiel die Taktfrequenz, mit der ein PC- oder Server-Prozessor arbeitet (also die Anzahl von Transaktionen, welche die auf ihm enthaltenen Transistoren pro Sekunde durchführen) bereits seit 2005 nicht mehr wesentlich gesteigert werden. Bis dahin war die Taktfrequenz ein wichtiges Element, um die Leistungsfähigkeit von Prozessoren zu erhöhen. Hier wurde die Halbleiterindustrie zum ersten Mal ein „Opfer ihres eigenen Erfolgs“. Seit Jahrzehnten hat sie die Anzahl der Transistoren auf gleicher Fläche durch eine anhaltende Miniaturisierung alle 18 bis 24 Monate verdoppelt. Diese über einen langen Zeitraum gültige Regel, auch als „Moore‘s Law“ bekannt, führte dazu, dass die Anzahl der Transistoren eines Prozessors dramatisch anstieg. Von 2250 Transistoren beim „Intel 4004“, dem ersten kommerziellen Mikroprozessor aus dem Jahr 1971, auf bis zu 115 Milliarden (!) bei modernen Prozessoren. Die stark steigende Anzahl an immer kleineren Transistoren auf gleichbleibender Fläche führte bei steigender Taktfrequenz aber zu einer starken Erwärmung des Prozessors. Um eine Beschädigung des Chips zu verhindern, hätte es einer aufwendigen und teuren Kühlung bedurft. Da diese zu einem deutlichen Anstieg der Systemkosten und des Stromverbrauchs geführt hätte, haben Prozessorhersteller wie Intel und AMD ab 2005 daher primär auf eine weitere Erhöhung der Transistorenanzahl bei gleicher Chipgröße gesetzt. Die Taktfrequenz blieb hingegen nahezu konstant. Sie liegt bei den meisten Prozessoren bei 3,5 bis 4,5 Gigahertz. Das heißt, sie können 3,5 bis 4,5 Milliarden Instruktionen pro Sekunde ausführen.

Als Ausgleich für die fehlende Möglichkeit, die Leistungsfähigkeit ihrer Prozessoren über die Taktfrequenz zu erhöhen, haben die Prozessorhersteller mehrere Prozessorkerne auf einem Chip zusammengefasst. Damit konnte die Leistungsfähigkeit neben der steigenden Anzahl von Transistoren im ähnlichen Ausmaß wie in der Vergangenheit erhöht werden. Die sogenannten „Multi-Core“ Systeme sind inzwischen Standard. Im PC-Bereich sind heute 6 Kern-Prozessoren üblich. Das Spitzenprodukt von Intel verfügt gar über 24 parallel arbeitende Kerne.

Im Vergleich dazu bewegt sich Nvidia in völlig anderen Dimensionen: Die auf der Technologie von Graphikkarten basierenden Prozessoren von Nvidia verfügen über die unglaubliche Zahl von nahezu 16.400 einzelnen Kernen, die dank einer speziellen Chiparchitektur und Software besonders effizient miteinander arbeiten. So sind die Nvidia-Prozessoren besonders geeignet für den Einsatz im Bereich der künstlichen Intelligenz, wo man mit neuronalen Netzen versucht, die menschlichen Gehirnfunktionen nachzubauen.

Aber das nächste Problem bei der Fortschreibung von Moore’s Law erscheint langsam am Horizont: Auch das Schrumpfen der Transistoren stößt in einigen Jahren an seine physikalischen Grenzen. Noch gelingt es durch die neue Generation von Lithographie-Maschinen des niederländischen Unternehmens ASML – sie basieren auf extrem ultraviolettem Licht (EUV), mit dem man sehr dünne Strukturen auf den Wafer projizieren kann – noch leistungsfähigere Prozessoren zu erzeugen. Dies ist allerdings technisch kompliziert und mit hohen Kosten verbunden. Unter einem Nanometer (entspricht einem Milliardstel Meter beziehungsweise einem Siebzigtausendstel eines Menschenhaars) als Breite einer Schaltung dürfte die klassische Halbleitertechnik auf Siliziumbasis Mitte des kommenden Jahrzehnts weitgehend ausgereizt sein.

Auch danach lässt sich Moore‘s Law dank dem Einsatz neuer Materialien wie 3D- Kohlenstoffnanoröhrchen oder Wolframsulfid sicher weiter fortsetzen. Und dann könnte irgendwann die Zeit der Quantencomputer kommen, die nicht mehr auf dem traditionellen Ein/Aus-Prinzip klassischer Halbleiter basieren.

Der Königsweg der nächsten Jahre, die Leistungsfähigkeit von Halbleitern zu steigern, beruht aber auf einer anderen Idee: Man packt mehrere, oft verschiedene, Halbleiter zu einem Chip zusammen. Mit anderen Worten: Man spart sich den „Umweg über die Leiterplatte“ und erreicht damit eine deutlich schnellere Kommunikation der Bauteile miteinander. So werden häufig, insbesondere für KI-Anwendungen, Prozessoren mit schnellen Speicherchips (sogenannten „HBM“ = High Bandwidth Memories) in einem Package zusammengebracht. Diese sind oft als sogenannte „Chiplets“ bereits für die Verbindung in einem Halbleiter-Package konzipiert. Bringt man weitgehend gleiche Bauteile zusammen, bezeichnet man dies als „System on Chip“ (SOC). Hierunter fallen auch die oben erwähnten Prozessoren mit mehreren Kernen.

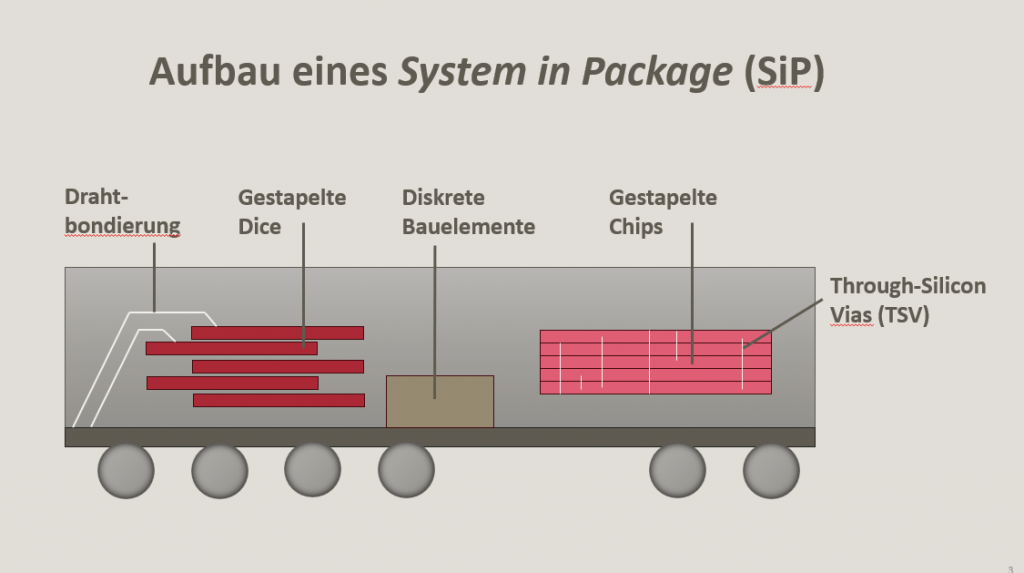

Der Trend geht aber dazu, unterschiedliche Bauteile wie Prozessoren und Speicherchips, aber auch Sensoren, Security Chips, Kommunikationschips, MEMS (mikromechanische Bauteile), passive Bauelemente und Antennen in einem Package zusammenzubringen. Diese sogenannte „System in Package“ (SIP)-Technologie bringt neben einer deutlichen Leistungssteigerung aufgrund der kurzen Wege zwischen den einzelnen Bauteilen noch weitere Vorteile wie Produktionskosten-, Platz- und Stromersparnisse.

Quelle: itwissen.info

Zur Erstellung von „System in Package“-Lösungen bedarf es neuer Methoden, um Halbleiter miteinander zu verbinden. Dem früher eher unbedeutenden Schritt, den fertigen Halbleiter mit einer Schutzhülle zu umgeben und Anschlussmöglichkeiten zur „Außenwelt“ zu montieren, kommt damit eine ganz neue Bedeutung zu. Die neuen Arbeitsschritte sind deutlich komplizierter als das klassische „Verpacken“ eines Halbleiters, zumal die einzelnen Chips häufig auch dreidimensional verbunden werden. Die hierfür notwendige Technologie wird als „Advanced Packaging“ bezeichnet und umfasst zahlreiche Einzeltechnologien, die je nach Eigenschaft des jeweiligen Bauteils und seinem Einsatz im System genutzt werden.

Die großen Halbleiterhersteller sehen „Advanced Packaging“ als neues Paradigma der Halbleiterindustrie und entscheidend dafür, dass Moore’s Law zumindest aus Sicht der Leistungsfähigkeit der zukünftigen Halbleiter weiter Bestand hat. So hat das Unternehmen TSMC mit „COWOS“ (Chip on Wafer on Substrate) eine Technologie entwickelt, mit der Graphikprozessoren wie die von NVIDIA mit sechs leistungsstarken Speicherchips verbunden werden. Die Nachfrage nach COWOS-Lösungen ist so hoch, dass TSMC seine Kapazitäten hierfür in den kommenden 18 Monaten verdreifachen wird. Auch Intel geht neue Wege und trennt bei seinen Prozessoren die Transistoren und ihre Stromversorgung, die über die Rückseite des Chips dann in einem Package angebunden wird. Die sogenannte „Backside Power Delivery“ ermöglicht mehr Transistoren auf der von der Stromversorgung befreiten Vorderseite und verbraucht weniger Energie bei der nun großzügig gestaltbaren Stromversorgung. Intel wird mit dieser Technologie in 2024 in Serie gehen. TSMC will hier bis 2026 nachziehen.

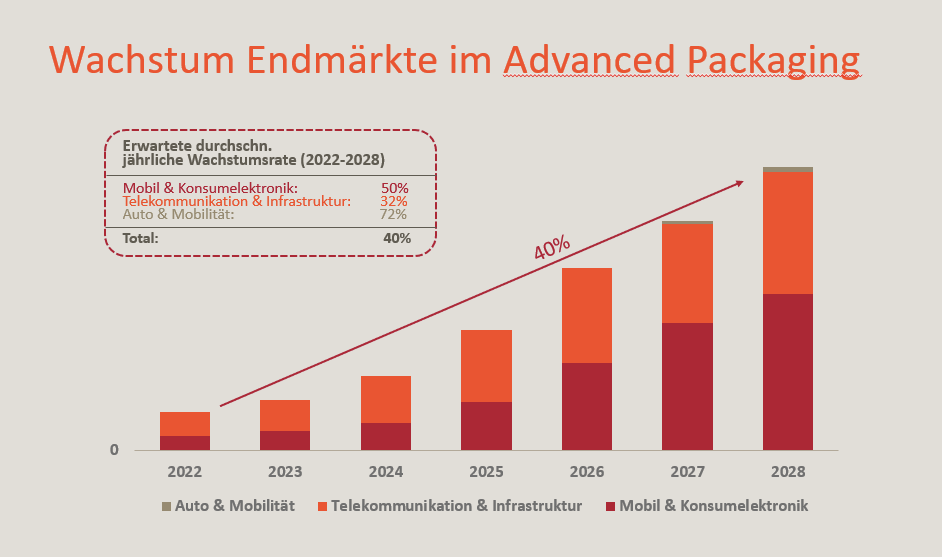

Das sind nur zwei prominente Beispiele für den Einsatz von Advanced Technology Anwendungen. Bisher kommen diese Lösungen primär nur im Server-Bereich zum Einsatz. In den nächsten Jahren dürften „SIP“-Lösungen aber in nahezu allen Halbleitereinsatzfeldern zum Einsatz kommen. Der Markt für Advanced Packaging soll daher auch um 40% pro Jahr wachsen und sich damit bis zum Jahr 2028 nahezu vervierfachen.

Die Halbleiterausrüster, die für Advanced Packaging die richtigen Lösungen anbieten, werden daher ebenfalls stark wachsen. Hier finden wir in Europa wieder sehr gut positionierte Unternehmen, die insbesondere bei neuen Verbindungstechnologien wie dem sogenannten Hybrid-Bonding gut aufgestellt sind. Andere Unternehmen sind führend bei Chiplets im Kommunikationsbereich, oder setzen die neuen Verpackungstechnologien bereits in ihren Produkten ein. Da Advanced Packaging erst am Anfang steht, sehen wir für all diese Unternehmen noch erhebliche Wachstumspotentiale. Ein weiterer Grund, dass wir uns mit unserer starken Positionierung im Halbleitersektor sehr wohl fühlen, zumal der Sektor in 2024 vor einem zyklischen Aufschwung stehen sollte!

Sehr geehrte Investierende und Freunde/Freundinnen von APUS Capital,

der Bereich des Packagings, der früher nur ein wenig beachteter Nebenspielplatz bei der Erstellung von Halbleitern war, gewinnt durch neue Technologien erheblich an Bedeutung. Aus dem hässlichen Entlein wird ein schöner Schwan. Im ohnehin strukturell stark wachsenden Halbleitermarkt ergeben sich damit interessante Investitionsmöglichkeiten, die wir gerne für Sie nutzen wollen. Denn wir sind fest davon überzeugt: Halbleiter sind das Gold der Digitalisierung!

Mit besten Grüßen von den Mauerseglern aus Frankfurt!

Dr. Wolfram Eichner, Jürgen Kaup, Stefan Meyer, Johannes Ries, Uwe Schupp, Dr. Roland Seibt und Heinz-Gerd Vinken